Semiconductor

SB16C1054_TQ80

– 256 Byte Tx/Rx Deep FIFOs

– Dedicated 2 Control Pins for RS422 and RS485 Bus Auto

Control

– Data Rate up to 5.3Mbps

– Global Interrupt and Interrupt Vector Processing

– H/W and S/W Flow Control (Auto-RTS/CTS and Xon/Xoff)

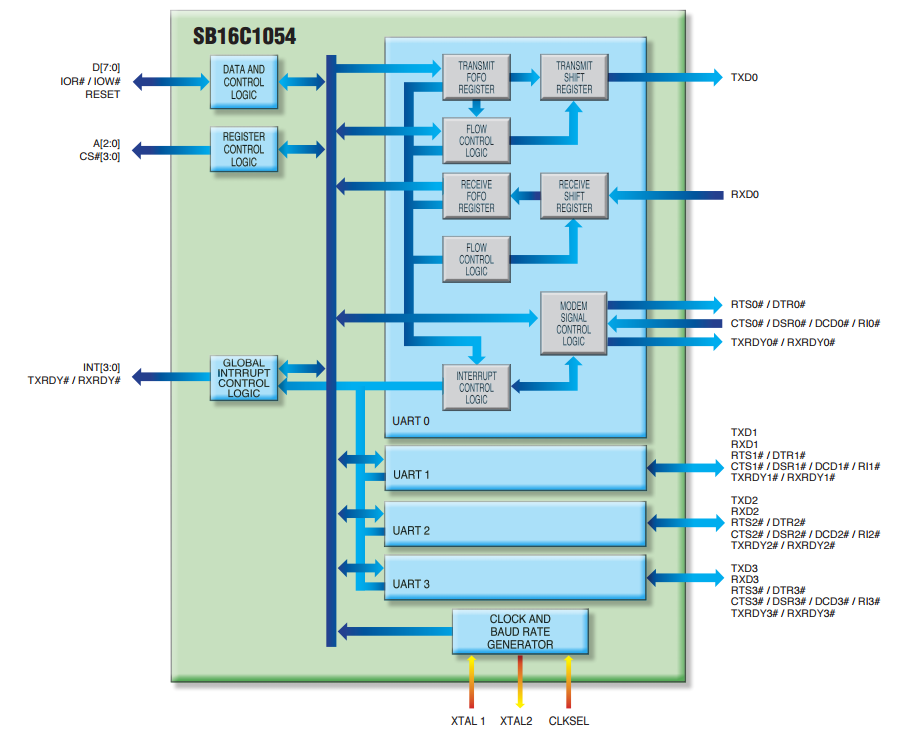

SB16C1054 is a Quad-UART (Universal Asynchronous Receiver and Transmitter) with 256-byte FIFOs, automatic hardware/software flow control, and can transmit and receive the data up to 5.3 Mbps. The 256-byte FIFOs reduce CPU overhead, allowing higher data rate and data throughput. In addition to the increased FIFO size and data rate, SB16C1054 also provides the enhanced features. It has the registers for reducing interrupt signal control logic and storing threshold levels of receive FIFO to start/stop transmission during hardware and software flow control.

Advanced Features

SB16C1054 has many advanced features which can be applied to various circuits. Each functions facilitates easier development, and simple but powerful circuit design. The functions specified below are only a portion of the powerful functions of Quad-UART, SB16C1054. Please visit our website and refer to the SB16C1054 data sheet for further information at http://www.sbchip.com/

256-byte FIFO

SB16C1054 has 256-byte TX/RX FIFOs to reduce CPU overhead for I/O. This large-FIFO will make your system more stable. There are two FIFO modes; 64-byte FIFO and 256-byte FIFO. The FCR (FIFO Control Register) and AFR (Additional Feature Register) enable FIFO and the Transmit Interrupt Trigger Level can be selected by the registers.

Fully Prioritized Interrupt System Control

Fully Prioritized Interrupt System Control have four independent 1-channel UARTs in SB16C1054 and four interrupts are available. The interrupts INT0, INT1, INT2 and INT3 are assigned to each channels. Each interrupt has six prioritized levels of interrupt generation capability. SB16C1054 can handle four interrupts with global interrupt. The global interrupt treats each of the four interrupts as a single interrupt, which is useful when an external system has a few interrupt resources.

Programmable Baud Rate Generator

SB16C1054 has a programmable baud rate generator with a pre-scaler. The pre-scaler is controlled by a register. This register sets the pre-scaler to divide a clock frequency to 1 or 4. And the baud rate generator further divides this clock frequency through a programmable divisor between 1 and 2^16-1 (or 65535) to obtain a x16 sampling rate clock of the serial data rate. The sampling rate clock is used by the transmitter for data bit shifting and receiver for data sampling.

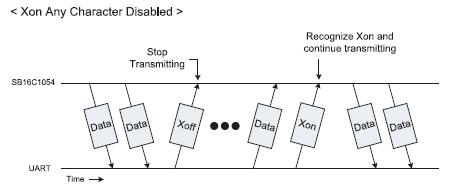

Xon Any Character Function

While RX software flow control function is activated, the data in TX FIFO are transmitted when Xon character arrives, and transmission is suspended when Xoff character arrives. This status is called ‘Xoff status’. Transmission is restarted when status changes to ‘Xon status’ by incoming Xon character or Xon Any function that changes status when any data arrives.

Xoff Re-transmit Function

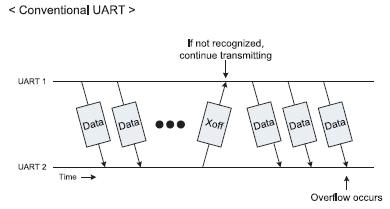

While TX software flow control function is activated, Xoff character is transmitted when the number of data exceeds a certain value. Though the external UART receives Xoff character, this character may not be recognized for some reasons and the data transmission may be continued. In this case, overflow may occur in RX FIFOs. Unlike the conventional UARTs, SB16C1054 can handle this with the Xoff Re-transmit function.

Global Interrupt MASK/POLL Register

GICR (Global Interrupt Control Register) and GISR (Global Interrupt Status Register) in SB16C1054 are used to determine whether each interrupt generated at four 16C1050 is to be transmitted as a global interrupt or not, and to verify the generation of each interrupt from four 16C1050 UARTs.

Auto-RTS and Auto-CTS Function

SB16C1054 provides the Auto-RTS and Auto-CTS function. The EFR (Enhanced Feature Register) enables or disables this function. They assert or de-assert RTS and CTS signals automatically when the data in Transmit or Receive FIFO reach a certain level.

False Start Bit Detection

SB16C1054 can detect the false start bit when receiving the data. When the serial data arrives, the start bit is asserted to low and SB16C1054 recognizes it. And in the middle of the clock, SB16C1054 checks the start bit whether it keeps asserted-low. If it keeps low, SB16C1054 allows it a right start-bit and if it goes back high, SB16C1054 regards it as a false start bit.